FPGA IP

FPGA IP

Off the shelf certifiable IP

Pre-developed and standardized IP cores or blocks are immediately available for integration into your systems. Designed to meet specific regulatory or industry certification standards, these IPs save development time and costs while ensuring compliance and reliability for various applications.

The following IPs are available:

ARINC 818 TX/RX IP Cores

Multi-Gigabit Video Transmission for Avionics

Elix Systems’ ARINC 818 TX and RX IP Cores are specifically engineered for low-latency, multi-gigabit video transmission and reception in rugged, mission-critical avionics systems. Designed for seamless integration, our ARINC 818 IP Cores feature separate TX and RX channels with AXI4-Stream interface for video transfer and AXI4-Lite interface for configuration. Easily customizable to your Interface Control Document (ICD), our IP Cores support single-link and dual-link configurations on both copper and fiber mediums, particularly offering industry-leading proven support for dual-link transmission and reception on copper.

Category

Specification

Compliance

ARINC 818

AMD, Intel, Microchip

Architecture

Transmitter only, receiver only, or both

Single- or dual-link

Up to 4 stream per link

Line synchronous timings

Up to FC 8x rate (8.5 Gbps) using 8b10b encoding

Monochrome, RGB, RGBA, YCbCr

(optional IPs available for various video conversion)

AXI4-Stream (video transfer)

AXI4-Lite (configuration)

Embedded video timing generator operating in master or slave mode

Error detections (CRC, buffer overrun/underrun)

DO 254 Certification package on request

ARINC 429 TX/RX IP Cores

Reliable Avionics Bus

The ARINC 429 TX and RX IP Cores are designed for reliable digital communication between avionics systems and instruments. They support programmable data rates of 12.5 kbps and 100 kbps, featuring separate TX and RX channels with AXI4-Lite interface for easy integration. Key features include programmable parity, queuing or CVT mode reception with optional timestamping, and advanced error checks. Built-in test functionalities like loopback and TX/RX message counters ensure reliability.

Category

Specification

Compliance

ARINC 429

Data Rate

Programmable:

12.5 kbps (low-speed)

100 kbps (high-speed)

Interface

16 RX, 8TX

FIFO

32-bit wide, programmable depth

Programmable even, odd or none

Reception

Queuing or Label/SDI Current-Value-Table mode

Optional timestamp and interruption

Built-in test

Loopback

TX/RX counters

Word, gap, parity errors flags and counters

DO 254 Certification package on request

UART TX/RX IP Core

Universal Asynchronous Communication Bus

UART TX and RX IP Core are designed for robust serial communication, supporting RS-232, RS-422 and RS-485 half- and full-duplex protocols. For seamless system integration, our IP core is compatible with the existing TL16C750 driver. Key features include a fully programmable serial interface (word length, stop bits, parity type) via an AXI4-Lite interface, a programmable baud rate generator, prioritized interrupt system controls, and errors detection. Built-in test functionalities such as loopback and TX/RX message counters ensure reliability.

Category

Specification

Compliance

RS-232, RS-422, RS-485 half- and full-duplex

Transmitter and receiver

RS232, RS422, RS485 modes, switching via LTC2871

Baud Rate

Generator with 14,74 MHz reference clock:

1’200, 2’400, 4’800, 9’600, 19’200, 38’400, 57’600, 115’200, 230’400, 460’800, 921’600

Interface

AXI4-Lite

Serial characteristics

Programmable:

Word length: 5, 6, 7 or 8-bit

Stop bits: 1 or 2-bit

Parity bits: even, odd, none

Reception

16- and 64-byte FIFO mode

Prioritized interruptions

Built-in test

Loopback

TX/RX counters

Parity. Overrun, framing errors flags and counters

DO 254 Certification package on request

DSI/O IP Core

Discrete Signal I/Os control

Elix Systems’ Discrete Signal Input/Output (DSI/O) IP Core enables the continuous capture and control of up to 32 independent inputs and outputs. Logic levels are readable and configurable through internal registers accessible via an AXI4-Lite interface, ensuring seamless integration and precise control. Built-in test functionalities such as loopback and stuck-at-fault detection ensure reliability.

Category

Specification

DSI only, DSO only or both

I/OS number

Up to 32 inputs/outputs per DSI/DSO

Interface

AXI4-Lite

Built-in test

Loopback

Stuk-at-fault detection

DO 254 Certification package on request

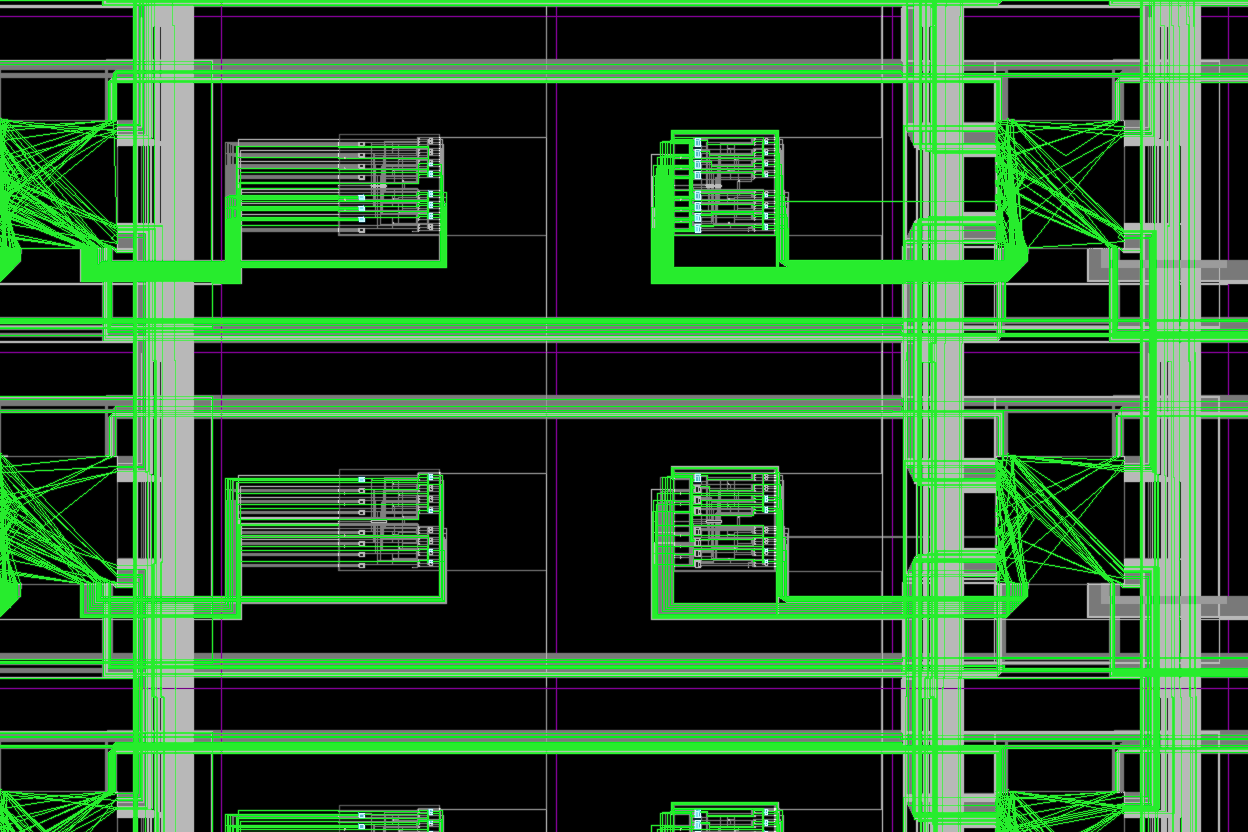

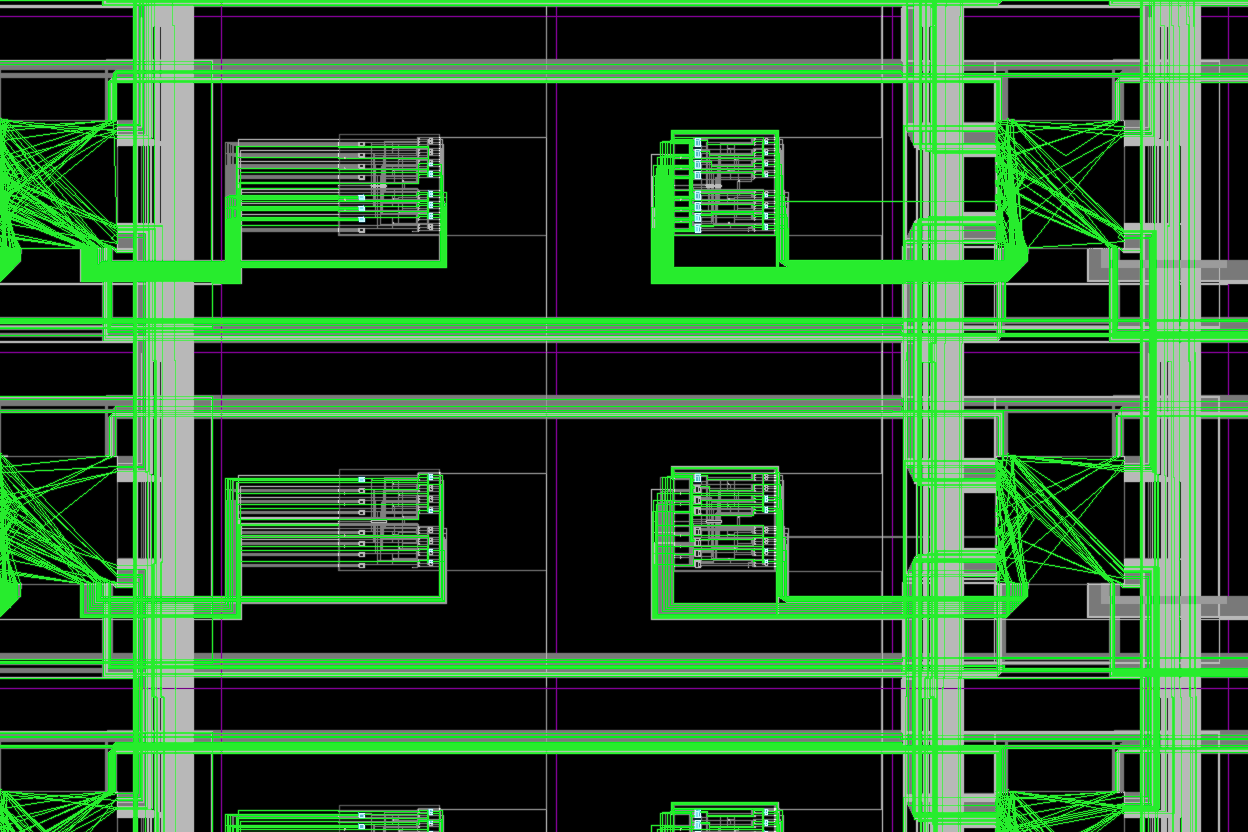

Video AXI DMA IP Core

Real-time high-resolution video frames grabber

Our Video AXI DMA IP Core is meticulously engineered for the efficient and continuous transfer of real-time video streams via DMA through an AXI4 master interface. Designed for seamless integration, this IP core features up to eight AXI4-Stream interfaces for video inputs and an AXI4-Lite slave interface for configuration. Paired with the AMD AXI Bridge for PCI Express Gen3 x8, our IP Core can transfer up to 8x 1080p60 video streams in real-time. Discover the power of our superior real-time high-resolution video frame grabber with this robust and versatile solution.

Category

Specification

Video Interface

Up to AXI4-Stream input interfaces

(optional IPs available for various video conversion)

Up to 8x DMA channels

Four frame buffers per DMA channel

Interface

AXI4 for DMA transfer

AXI4-Lite for configuration

Per DMA channel PCIe MSI interruption generation when a frame buffer is fully available

Endianness (little, big), packing, pixel width (16-bit, 24-bit, 32-bit), burst length

DO 254 Certification package on request